Miért rossz a RISC-V? ...

Forrás: https://news.ycombinator.com/item?id=24459195+ adrian_b on Sept 13, 2020

Ezt már sokszor megvitatták az internet számos fórumán.

Az összegzés az, hogy a RISC-V nem hatékony, mert több utasítást igényel ugyanahhoz a munkához, mint más ISA-k, és nincs olyan előnye, amely ellensúlyozná ezt a hibát.

Ezek az extra utasítások különösen szinte minden ciklusban megjelennek, és a legfontosabb ok az, hogy a RISC-V rosszabb címzési módokkal rendelkezik, mint a több mint 60 évvel ezelőtti vákuumcsöves számítógépek, amelyek csak néhány ezer csőből épültek, szemben a mostani több millió vagy milliárd tranzisztorral, amelyek egy CPU-hoz rendelkezésre állnak.

A RISC-V ISA ezen hibája miatt az Alibaba csapatának, amely a jelenleg legnagyobb teljesítményű RISC-V implementációt tervezte (Xuantie910, amelyet a múlt hónapban mutattak be a Hot Chips-en), egy egyedi ISA-bővítést kellett hozzáadnia további címzési módokkal, hogy elfogadható sebességet tudjon elérni.

Amikor a RISC-V ISA tervezőit kritizálják, azt válaszolják, hogy a nagyobb számú utasítás nem fontos, mert minden nagy teljesítményű implementációnak utasításfúziót kell végeznie, hogy elérje más ISA-k IPC-jét.

Ez azonban két okból is téves, az utasításfúzió nem képes csökkenteni a nagyobb kódméretet a nem hatékony utasításkódolás miatt, és a több utasítás párhuzamos dekódolásához és az utasításfúzió végrehajtásához szükséges hardver sokkal összetettebb, mint a kevesebb utasítás jobb kódolású dekódolásához szükséges hardver, mint más ISA-kban.

++ zozbot234 on Sept 13, 2020

> Mindazonáltal ez 2 okból rossz, az utasításfúzió nem tudja csökkenteni a nagyobb kódméretet a nem hatékony utasításkódolás miatt.

A RISC-V tartalmaz egy olyan tömörített kiterjesztést, amely az utasításkódolást versenyképessé vagy jobbá teszi az x86(!)-nál, és az ARM Thumb üzemmódjainak hátrányai nélkül.

+++ adrian_b on Sept 13, 2020

A tömörítési módszerek csökkentik a kód méretét, de ez nem számít az alaputasítás kódolásának hatékonyságát értékelve.

Ha ugyanezeket a tömörítési módszereket egy kompaktabb eredeti kódolásra alkalmaznánk, akkor a tömörített kód még kisebb lenne.

A konkurens ISA-k, például az ARM (Thumb), a MIPS (nanoMIPS) és a POWER szintén rendelkeznek tömörített kódolási változatokkal.

++++ ... (A vita itt még folytatódik, de nem érdekes.)

Saját megjegyzések a fentiekhez:

A MIPS architektúra a megszűnéséhez közelít: még létezik, de a fejlesztése megállt: a processzorgyártó cégek nem fejlesztenek újabb MIPS architektúrájú processzorokat (a kínaiak kivételével).

Az ARM Thumb utasításkészlet használatához a 32 bites rendszerekben egy üzemmód-átkapcsolás szükséges. Az ARM 64 bites rendszerekből ezt teljesen kihagyták: ezekben nincs Thumb üzemmód vagy tömörített utasításkódolás.

A POWER architektúrában a 2.07 verzióban jelent meg a VLE tömörített utasításkészlet, 2013-ban. Ez 4 címzési módot támogat és 32 és 16 bites utasításai vannak. Célja a kódsűrűség növelése a beágyazott rendszerekben.

A RISC-V utasításkészletben a tömörített utasítások eleve az ISA részét képezik (C jelű kiterjesztés), azokhoz nem kell üzemmódváltás.

A RISC-V utasításkészlet 3 címzési móddal rendelkezik: PC-relatív, regiszter-offszet, abszolút.

„Ezek a címzési módok gondosan lettek kiválasztva annak érdekében, hogy lehetővé tegyék a hatékony kódgenerálást minimális hardverkomplexitás mellett.” -- írja erre a SiFive ...

[]

A világ első asztali PC RISC-V alaplapja találkozik az AMD Radeon RX 6700 XT-vel

Anton Shilov,

Tom's Hardware, 2021-07-22T18:24:54+00:00

utoljára frissítve 2021 július 23.

(Kép: AMD)

(Kép: AMD)

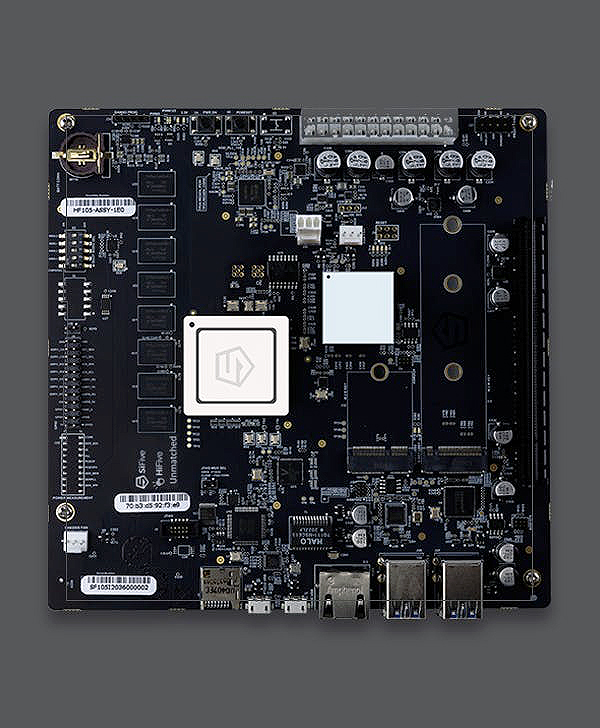

Amikor a SiFive tavaly bemutatta HiFive

Unmatched elnevezésű fejlesztőknek

szánt RISC-V asztali alaplapját,

már a kezdetektől fogva világos volt, hogy előbb-utóbb egy rajongó

megpróbálja majd olyasmire használni az U7-es SoC-jét, amire nem való:

általános PC-s használatra, nagy teljesítményű grafikával és

videódekódolással. Ez az idő eljött, mivel egy rajongónak sikerült az

AMD Radeon RX 6700 XT-t Linux alatt RISC-V SoC-vel működésre

bírnia.

René Rebe informatikus úgy döntött, bebizonyítja, hogy a SiFive HiFive

Unmatched nemcsak Linuxot tud futtatni, hanem nagy teljesítményű

grafikus processzort is tud használni – számol be a Hackster.io.

Ehhez 10 órát töltött a Linux kernel foltozásával, hogy támogatást adjon

az AMD Radeon RX 6700 XT grafikus kártyához, valamint a Mesa Gallium

21.1.5 vezérlőhöz.

Rebe nemcsak azt érte el, hogy az AMD Radeon RX 6700 XT megjelenítse a Linux grafikus felhasználói felületét, hanem még a 3D grafika hardveresen gyorsított módban történő megjelenítését és a videó dekódolását is elérte. Játékokat nem próbált indítani (a videódekódolással kapcsolatban vannak bizonyos korlátok), de mivel ez a világ első kísérlete arra, hogy egy nagy teljesítményű GPU-t RISC-V processzorral működtessen, a vállalkozás sikeresnek tekinthető.

(Kép: SiFive)

(Kép: SiFive)A SiFive HiFive Unmatched lapkája a Freedom U740 SoC-vel

rendelkezik a PC felhasználók által megszokott összes PC I/O

interfésszel, beleértve a PCIe 3.0 x8/16, M.2 slotokat és USB portokat.

Ennek érdekében a HiFive Unmatched lapka által működtetett PC-be szinte

bármilyen modern hardvert be lehet építeni. Végül is az alaplapot olyan

fejlesztők számára tervezték, akik a közelgő RISC-V SoC-khez készült

kliens PC- és szerverszoftvereken dolgoznak. Van azonban egy korlátozás:

a Linux nem támogatja megfelelően a RISC-V-t, mivel a legtöbb

RISC-V-alapú chip mikrokovezérlő, amely nem képes magas szintű operációs

rendszereket futtatni. Bár vannak olyan RISC-V SoC-k, amelyek képesek

futtatni őket (pl. a Freedom U740), ezek nem különösebben gyorsak.

A SiFive Unmatched RISC-V alaplapjáról, az AMD Radeon RX 6700 XT-vel végzett kísérletről további részletek a Bits inside by René Rebe YouTube csatornán találhatók.